Understanding the differences between capacitance in series vs parallel is pivotal for both electrical engineering students and professionals. The two configurations serve different purposes and exhibit distinct electrical properties that are essential for optimizing circuit designs. To provide clarity, this article delves into these differences from an expert perspective, backed by practical insights and evidence-based statements.

Key insights box:

Key Insights

- Capacitance in series and parallel differs fundamentally in terms of total capacitance calculation and overall circuit behavior.

- While capacitance in series results in a total value that is less than the smallest individual capacitor, in parallel, the total value is always greater than any single capacitor.

- Choosing the correct configuration is crucial for optimizing the performance of electronic circuits.

The nuances of how capacitors behave in series versus parallel have significant implications for electronic circuit design and optimization. Let’s first explore the concept of capacitance in series.

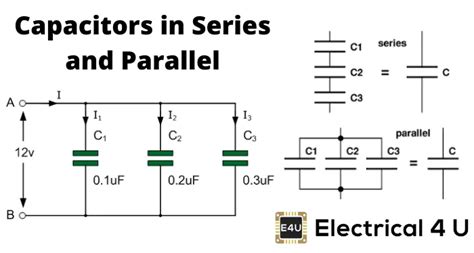

In a series configuration, capacitors are connected end-to-end, forming a single path for current to flow. The primary insight here is that the total or equivalent capacitance (C_eq) in series is always less than the smallest individual capacitor’s value. Mathematically, the reciprocal of the total capacitance in series is the sum of the reciprocals of each capacitor’s value:

1/C_eq = 1/C1 + 1/C2 + 1/C3 +...

This relationship results from the fact that a capacitor in series limits the overall charge storage capability. For instance, if you have three capacitors of 10 µF, 20 µF, and 30 µF in series, the equivalent capacitance is calculated as:

1/C_eq = 1/10 + 1/20 + 1/30 = 0.15

Thus, C_eq = 6.67 µF. This illustrates a critical technical consideration: in series configurations, the equivalent capacitance decreases, which can be problematic for circuits requiring a specific capacitance value for energy storage or filtering.

In contrast, when capacitors are connected in parallel, they share the same voltage across their plates, but each capacitor contributes to the overall charge storage. The total or equivalent capacitance (C_eq) in parallel is the sum of the individual capacitances:

C_eq = C1 + C2 + C3 +...

For example, if you have capacitors of 10 µF, 20 µF, and 30 µF connected in parallel, the equivalent capacitance is:

C_eq = 10 + 20 + 30 = 60 µF

In this setup, the equivalent capacitance increases with each additional capacitor, providing a higher charge storage capacity. This can be particularly beneficial in applications requiring high capacitance values, such as in power supply filters or energy storage systems.

To sum up, understanding the fundamental differences between capacitance in series vs parallel has practical applications in designing efficient electronic circuits. Series configurations are beneficial when minimizing space or voltage levels are a concern, while parallel setups offer enhanced capacitance values suitable for high-demand storage and filtering applications.

FAQ section

What is the effect of capacitance values on total capacitance in series?

In a series configuration, the total or equivalent capacitance is always less than the smallest individual capacitor value due to the reciprocal sum formula. This decreases the overall charge storage capability compared to individual capacitors.

How does capacitance in parallel differ from series in terms of total capacitance?

In parallel configurations, the total or equivalent capacitance is the sum of the individual capacitance values, always resulting in a higher total value than any single capacitor. This increases the overall charge storage capacity significantly.

This article has elucidated the fundamental differences between capacitance in series and parallel, providing practical insights and actionable recommendations for optimizing circuit designs. With a clear understanding of these concepts, engineers and students can better tailor their circuit designs to meet specific performance requirements.